#### NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

## DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

# **COURSE MATERIALS**

# CS 404 EMBEDED SYSTEMS

#### VISION OF THE INSTITUTION

To mold true citizens who are millennium leaders and catalysts of change through excellence in education.

## MISSION OF THE INSTITUTION

**NCERC** is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mold technically competent citizens with moral integrity, social commitment and ethical values.

We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mold them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

## **ABOUT DEPARTMENT**

- Established in: 2002

- Course offered : B.Tech in Computer Science and Engineering

M.Tech in Computer Science and Engineering

M.Tech in Cyber Security

- Approved by AICTE New Delhi and Accredited by NAAC

- ◆ Affiliated to the University of A P J Abdul Kalam Technological University.

## **DEPARTMENT VISION**

Producing Highly Competent, Innovative and Ethical Computer Science and Engineering Professionals to facilitate continuous technological advancement.

## **DEPARTMENT MISSION**

- 1. To Impart Quality Education by creative Teaching Learning Process

- 2. To Promote cutting-edge Research and Development Process to solve real world problems with emerging technologies.

- 3. To Inculcate Entrepreneurship Skills among Students.

- 4. To cultivate Moral and Ethical Values in their Profession.

- 5.

#### PROGRAMME EDUCATIONAL OBJECTIVES

- **PEO1:** Graduates will be able to Work and Contribute in the domains of Computer Science and Engineering through lifelong learning.

- **PEO2:** Graduates will be able to Analyze, design and development of novel Software Packages, Web Services, System Tools and Components as per needs and specifications.

- **PEO3:** Graduates will be able to demonstrate their ability to adapt to a rapidly changing environment by learning and applying new technologies.

- **PEO4:** Graduates will be able to adopt ethical attitudes, exhibit effective communication skills, Teamwork and leadership qualities.

#### **PROGRAM OUTCOMES (POS)**

#### Engineering Graduates will be able to:

- 1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

#### PROGRAM SPECIFIC OUTCOMES (PSO)

**PSO1**: Ability to Formulate and Simulate Innovative Ideas to provide software solutions for Realtime Problems and to investigate for its future scope.

**PSO2**: Ability to learn and apply various methodologies for facilitating development of high quality System Software Tools and Efficient Web Design Models with a focus on performance

Optimization.

**PSO3**: Ability to inculcate the Knowledge for developing Codes and integrating hardware/software products in the domains of Big Data Analytics, Web Applications and Mobile Apps to create innovative career path and for the socially relevant issues.

## **COURSE OUTCOMES**

| CO1 | Demonstrate the role of individual components involved in a typical embedded system                                    |

|-----|------------------------------------------------------------------------------------------------------------------------|

| CO2 | Analyze the characteristics of different computing elements and select the most appropriate one for an embedded system |

| CO3 | Model the operation of a given embedded system.                                                                        |

| CO4 | Substantiate the role of different software modules in the development of an embedded system                           |

| CO5 | Develop simple tasks to run on an RTOS                                                                                 |

| CO6 | Examine the latest trends prevalent in embedded system design                                                          |

## MAPPING OF COURSE OUTCOMES WITH PROGRAM OUTCOMES

|     | РО |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|

|     | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 |

| CO1 | 3  | 2  | 1  |    |    |    |    |    |    | 3  |    | 3  |

| CO2 | 3  | 2  | 1  | 2  |    |    |    |    |    | 3  |    | 3  |

| CO3 | 3  | 2  | 1  | 2  |    |    |    |    |    | 3  |    | 3  |

| CO4 | 3  | 2  | 1  | 2  |    |    |    |    |    | 3  |    | 3  |

| CO5 | 3  | 3  | 2  |    |    |    |    |    |    | 3  |    | 3  |

| CO6 | 3  | 3  | 2  |    |    | 2  |    |    |    | 3  |    | 3  |

## Note: H-Highly correlated=3, M-Medium correlated=2, L-Less correlated=1

## **CO PSO Mapping**

| CO'S   | PSO1 | PSO2 | PSO3 |

|--------|------|------|------|

| C412.1 | 3    | 3    | -    |

| C412.2 | 2    | 2    | 3    |

| C412.3 | 2    | -    | -    |

| C412.4 | -    | -    | 3    |

| C412.5 | 3    | 3    | 3    |

| C412.6 | 3    | -    | 3    |

## SYLLABUS

| Course<br>code                                                                                       | Course Name                                                                     | L-T-P -Credits          | Year of<br>Introduction |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------|-------------------------|--|--|--|--|--|

| CS404                                                                                                | Embedded Systems                                                                | 3-0-0-3                 | 2016                    |  |  |  |  |  |

| Course O                                                                                             | jectives:                                                                       |                         |                         |  |  |  |  |  |

| <ul> <li>To introduce the technologies behind embedded computing systems.</li> </ul>                 |                                                                                 |                         |                         |  |  |  |  |  |

| <ul> <li>To introduce and discuss various software components involved in embedded system</li> </ul> |                                                                                 |                         |                         |  |  |  |  |  |

| design and development.                                                                              |                                                                                 |                         |                         |  |  |  |  |  |

|                                                                                                      | expose students to the recent trends in                                         | embedded system des     | sign.                   |  |  |  |  |  |

| Syllabus:                                                                                            |                                                                                 |                         |                         |  |  |  |  |  |

|                                                                                                      | n to embedded systems, basic c                                                  |                         |                         |  |  |  |  |  |

|                                                                                                      | systems, firmware development. Int                                              |                         |                         |  |  |  |  |  |

| -                                                                                                    | nt environment. Characteristics of R'<br>DS. Embedded product development 1     |                         | ng, creating tasks in a |  |  |  |  |  |

| Expected                                                                                             | · · ·                                                                           | ne cycle.               |                         |  |  |  |  |  |

|                                                                                                      | t will be able to :                                                             |                         |                         |  |  |  |  |  |

|                                                                                                      | monstrate the role of individual co                                             | mponents involved i     | n a typical embedded    |  |  |  |  |  |

|                                                                                                      | stem                                                                            | 1                       | 71                      |  |  |  |  |  |

| -                                                                                                    | alyze the characteristics of differen                                           | t computing element     | s and select the most   |  |  |  |  |  |

| aj                                                                                                   | propriate one for an embedded system                                            | 1                       |                         |  |  |  |  |  |

|                                                                                                      | odel the operation of a given embedde                                           |                         |                         |  |  |  |  |  |

|                                                                                                      | bstantiate the role of different soft                                           | tware modules in th     | e development of an     |  |  |  |  |  |

|                                                                                                      | ibedded system                                                                  |                         |                         |  |  |  |  |  |

|                                                                                                      | velop simple tasks to run on an RTOS<br>amine the latest trends prevalent in en |                         |                         |  |  |  |  |  |

| vi. ez<br>Reference                                                                                  |                                                                                 | indeduced system design | 1                       |  |  |  |  |  |

|                                                                                                      | taunstrup and Wayne Wolf, Hardw                                                 | are / Software Co-E     | Design: Principles and  |  |  |  |  |  |

|                                                                                                      | ctice, Prentice Hall.                                                           |                         | engin rinnepite and     |  |  |  |  |  |

|                                                                                                      | J. Labrose, Micro C/OS II: The Real                                             | Time Kernel 2e CR       | C Press 2002            |  |  |  |  |  |

|                                                                                                      | Kamal, Embedded Systems: Arch                                                   |                         |                         |  |  |  |  |  |

|                                                                                                      | tion, McGraw Hill Education (India),                                            |                         | s and besign, rind      |  |  |  |  |  |

|                                                                                                      | bu K.V., Introduction to Embedded                                               |                         | Hill Education (India)  |  |  |  |  |  |

| 4. 31                                                                                                |                                                                                 | Systems, weblaw I       | ini Education (India),  |  |  |  |  |  |

|                                                                                                      | -                                                                               | Second Edition Elson    | vier                    |  |  |  |  |  |

|                                                                                                      | we Heath, Embedded System Design,                                               |                         |                         |  |  |  |  |  |

|                                                                                                      | yne Wolf, Computers as Component                                                |                         | ided Computer System    |  |  |  |  |  |

| De                                                                                                   | ign, Morgan Kaufmann publishers, Tl                                             | mild edition, 2012.     |                         |  |  |  |  |  |

|                            | Course Plan                                                                                                                                                                                                                                                                                   |       |                              |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|--|--|

| Module                     | Contents                                                                                                                                                                                                                                                                                      | Hours | End<br>Sem.<br>Exam<br>Marks |  |  |

| I                          | Fundamentals of Embedded Systems- complex systems and<br>microprocessors- Embedded system design process<br>.Specifications- architecture design of embedded system-<br>design of hardware and software components- structural and<br>behavioural description.                                | 6     | 15%                          |  |  |

| II                         | Hardware Software Co-Design and Program Modelling –<br>Fundamental Issues, Computational Models- Data Flow<br>Graph, Control Data Flow Graph, State Machine, Sequential<br>Model, Concurrent Model, Object oriented model, UML                                                                | 9     | 15%                          |  |  |

| FIRST INTERNAL EXAMINATION |                                                                                                                                                                                                                                                                                               |       |                              |  |  |

| ш                          | Design and Development of Embedded Product – Firmware<br>Design and Development – Design Approaches, Firmware<br>Development Languages.                                                                                                                                                       | 6     | 15%                          |  |  |

| IV                         | Integration and Testing of Embedded Hardware and<br>Firmware- Integration of Hardware and Firmware. Embedded<br>System Development Environment – IDEs, Cross Compilers,<br>Disassemblers, Decompilers, Simulators, Emulators and<br>Debuggers.                                                | 6     | 15%                          |  |  |

|                            | SECOND INTERNAL EXAMINATION                                                                                                                                                                                                                                                                   |       |                              |  |  |

| V                          | RTOS based Design – Basic operating system services.<br>Interrupt handling in RTOS environment. Design Principles.<br>Task scheduling models. How to Choose an RTOS. Case<br>Study – MicroC/OS-II.                                                                                            | 9     | 20%                          |  |  |

| VI                         | Networks – Distributed Embedded Architectures, Networks<br>for embedded systems, Network based design, Internet<br>enabled systems. Embedded Product Development Life Cycle<br>– Description – Objectives -Phases – Approaches1. Recent<br>Trends in Embedded Computing.<br>END SEMESTER EXAM | 6     | 20%                          |  |  |

#### Question Paper Pattern

- 1. There will be FOUR parts in the question paper A, B, C, D

- 2. Part A

- a. Total marks : 40

- b. TEN questions, each have 4 marks, covering all the SIX modules (THREE questions from modules I & II; THREE questions from modules III & IV; FOUR questions from modules V & VI). All questions have to be answered.

#### 3. Part B

- a. Total marks : 18

- b. THREE questions, each having 9 marks. One question is from module I; one question is from module II; one question uniformly covers modules I & II.

- c. Any TWO questions have to be answered.

- d. Each question can have maximum THREE subparts.

#### 4. Part C

- a. Total marks : 18

- b. THREE questions, each having 9 marks. One question is from module III; one question is from module IV; one question uniformly covers modules III & IV.

- c. Any TWO questions have to be answered.

- d. Each question can have maximum THREE subparts.

- 5. Part D

- a. Total marks : 24

- b. THREE questions, each having 12 marks. One question is from module V; one question is from module VI; one question uniformly covers modules V & VI.

- c. Any TWO questions have to be answered.

- d. Each question can have maximum THREE subparts.

- There will be AT LEAST 50% analytical/numerical questions in all possible combinations of question choices.

## **QUESTION BANK**

|       | MODULE I                                                 |     |    |          |

|-------|----------------------------------------------------------|-----|----|----------|

| Q:NO: | QUESTIONS                                                | СО  | KL | PAGE NO: |

| 1     | Define a system and an Embedded system.                  | CO1 | K5 | 3        |

| 2     | Write the Classification of Embedded systems.            | CO1 | K3 | 4        |

| 3     | Write a note on Design metrics.                          | CO1 | K2 | 7        |

| 4     | Write a note on Complex systems & Microprocessors.       | CO1 | K3 | 8        |

| 5     | Describe Embedded hardware components                    | CO1 | K5 | 12       |

| 6     | List software components of an Embedded system.          | CO1 | K2 | 17       |

| 7     | Describe software tools for designing an embedded system | CO1 | K5 | 20       |

#### **MODULE II**

|   |                                                     |     |    | r  |

|---|-----------------------------------------------------|-----|----|----|

| 1 | Explain the Hardware software Co-design & Program   | CO2 | K2 | 24 |

|   | Modeling                                            |     |    |    |

| 2 | Define Data flow graph                              | CO2 | K4 | 31 |

| 3 | Explain the characteristics of Embedded system      | CO2 | K2 | 33 |

| 4 | Classify different design metrics in design process | CO2 | K5 | 35 |

| 5 | Explain Embedded system with neat block diagram.    | CO2 | K5 | 37 |

| 6 | Describe the issues in Hardware –Software Co-design | CO2 | K3 | 39 |

| 7 | Describe sequential model for ACVM.                 | CO2 | K5 | 42 |

## **MODULE III**

| 1 | Define Embedded firmware Design & Development. | CO3 | K3 | 48 |

|---|------------------------------------------------|-----|----|----|

| 2 | Describe the Embedded OS approach.             | CO3 | K3 | 50 |

| 3 | Describe the Embedded firmware development     | CO3 | K2 | 51 |

|   | Languages.                                     |     |    |    |

| 4 | Explain High Level Language based Development. | CO3 | K3 | 54 |

| 5 | Write a note on Mixing Assembly & High level   | CO3 | K5 | 55 |

|   | language.                                      |     |    |    |

| 6 | Explain Programming in Embedded C.             | CO3 | K3 | 56 |

| 7 | Write note on Compliler Vs Cross-Compiler      | CO3 | K2 | 57 |

|   |                                                |     |    |    |

## MODULE IV

| 1 | What is an OS?                                              | CO4 | K2 | 60 |  |  |

|---|-------------------------------------------------------------|-----|----|----|--|--|

| 2 | Explain Integration of H/w and Firmware.                    | CO4 | K1 | 63 |  |  |

| 3 | List the Types of files generated on Cross-<br>compilation. | CO4 | K2 | 67 |  |  |

| 4 | Short note on Disassembler /DE compiler                     | CO4 | K3 | 71 |  |  |

| 5 | Write note on Simulators, Emulators & Debugging             | CO4 | K1 | 72 |  |  |

| 6 | Describe Monitor Program Based Firmware<br>Debugging.       | CO4 | K2 | 75 |  |  |

| 7 | Explain the Embedded system Development<br>Environment.     | CO4 | K3 | 79 |  |  |

|   | MODULE V                                                    |     |    |    |  |  |

| 1 | List the types of Operating System.     | CO5 | K4 | 84 |

|---|-----------------------------------------|-----|----|----|

| 2 | Explain FIFO task scheduling            | CO5 | K2 | 85 |

| 3 | Write a note on Robin Round scheduling  | CO5 | K3 | 89 |

| 4 | Write a note on Functional Requirements | CO5 | K2 | 91 |

| 5 | Explain RTOS & Functions           | CO5 | K3 | 94 |

|---|------------------------------------|-----|----|----|

|   |                                    |     |    |    |

| 6 | Explain Interrupt Handling in RTOS | CO5 | K2 | 93 |

| 7 | Write RTOS Design Principles.      | CO5 | K2 | 98 |

|   |                                           | -   |    |      |

|---|-------------------------------------------|-----|----|------|

| 1 | Define Network Embedded Systems           | CO5 | K4 | `104 |

| 2 | Explain serial bus communication Protocol | CO5 | K2 | 106  |

| 3 | Describe CAN Bus and USB Bus              | CO5 | K3 | 107  |

| 4 | Define ISA Bus                            | CO5 | K2 | 109  |

| 5 | Define Internet Enabled systems           | CO5 | K3 | 111  |

| 6 | Explain TCP                               | CO5 | K2 | 112  |

| 7 | List the functions of UDP                 | CO5 | K2 | 112  |

## **MODULE NOTES**

- .

- .

- .

- CSE DEPARTMENT, NCERC PAMPADY

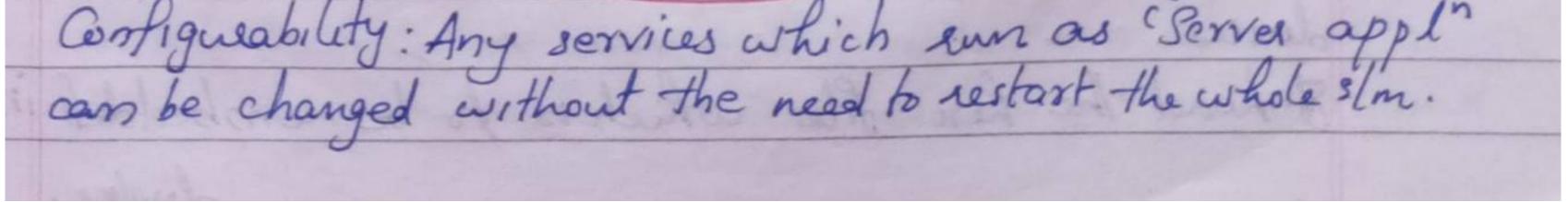

Fage No : MODULE I Introduction to Embedded System: > Understanding the Basic Concepts > Fundamentals of Embedded Slms > The typical Embedded System Design process - Characteristics - Architecture Lesign - Quality Atteibutes. N/w & s/w components. - Stauctural & behavioral description Question Bank: (Module 18 I). 1. Define à s/m & an Embedded S/m. x 2. List 3 main components of an Embedded S/m.x 3. White short notes on Computational models. 4. Define Costrol Data Flow Graph. 5. Demonstrate the role of individual components of involved in a typical embedded s/m. 6. Explain the challenges in Embedded S/m design. 7. Analyse the characteristics of diff. Pgm Models. 8. Classify duff. State Machines with eg: 9. Differentiate blu Concurrent Model & Object Oriented Model. 10. dentify the features of Seq. Model. Il. & Weite short notes on program models. 12. Define Data Flow Graph. 13. Define Miceoprocessor with basic Inal units. 14. Luit 3 main constraints on Embedded 8/m design. 15. Emplain the characteristics of Embedded S/m. 16. Discuss in detail about the classifich of Embedded s/m. 17. Explain design provers in Embedded Shm.

Scanned by TapScanner

19. Explain Regram Models. 20. Describe the characteristics of Sequential Data Flow Graph. 21. Differentiate 6/w Data Flow graph & Control Data flow graph 22. Define Small Scale Embedded System 23. List Diff. Computational Models. 24. White short notes on Object Oriented Model 25. Define State Machine. 26. Explain Characteristics of Embedded System. 27. Discuss in detail about the classification of Embedded System. 28. Explain the challenges in Embedded 3/m. 29. Explains & Embedded 8/m with neat Block diagram. 30. Discuss indetail about the concepts during the design pesses of Embedded Slm. 31. Esplain the abstraction of Embedded 8/m design plocess. 32. Describe the issues in R/w-s/w Co-Design. 33. Défine Concurrent Model with example. 34. Describe Sequestial Model for ACVM. 35. Explain l'éformance Accèle rators.

Fundamentals of Embedded Systems: System: A system is a way of working, organizing or doing one or many tasks acc. to a fisced plan, pgm, or set of rules. It is an arrangement in which all its units assemble and work together acc- to the plan or program Embedded System: In embedded system is a system that has embedded s/w & computer h/w, which makes it a s/m dedicated for an application or specific part of an appl' or product or part of a larger system. · Computer - components -> uprocessor, Large memory, 1/0 units, N/wing units, O.S. -An embedded s/m is a s/m that has 3 main components embedded into it: . 1. It embeds this similar to a computer Eq: 8/w embeds in the ROM or flash memory. 2. It embeds main appl s/w. 3. It embeds real-time OS. · Input Devices CLABS Interfacing/Driver clifs F Spee Processor Pgm Menery E Data Mem. Timers Apply Interrupt Serial comm ports Parallel ports 0/ps Interfacing !

Characteristics of Embedded System. An embedded s/m is characterized by the following: 1. Realhine & multisate operations define the ways in which the S/m works, seacts to events, interrupts, & shedules the S/m' furnchoning in seal time. For eg:, audio, video, data, shu stream & events have différent hatés à time constraints. 2) Complese Algorithms: 3) Complex Graphic user Interfaces 4) Dedicated functions. Constraints: A ling of the long to light An embedded 3/m is designed keeping in view 3 constraints: 1. available 8/m-memory 2. available processor - speed 3. The need to limit power dessipation Eg: wait for events, eun, stop, wake-up, sleep. 2. aft ensslads assain Electre the Share Classification of Embedded Systems: -> Embedded s/ms into 3 types: 1. Small Scale embedded stors: These stors are designed with a single 8 or 16 bit Ucteller; they have little h/w & sla complexities and involve board-level design They may be battery operated. The main pgming tools are an editor, assembler, cross assembler, an integrated development Environment specific to the Ucteller. 2. Médium scale embedded s/ms: These s/ms are designed with a single or a few single puepose processor 8, 16 or

Scanned by TapScanner

Sophisticated imbedded systems. These s/ms have enormous R/w & s/w complexities & may need several IPs, ASIPs, statable processors or configurable logic arrays. They are constrained by the processing speeds available in their R/w units. \_ cutting edge applications. As2p-> Application specific Design Process in Embedded System: Instruct processor The concepts used during a design process are as follouss: 1. Abstraction: Each peoblem component is first abstracted. For eq:, in the design of a Robotic 8/m, the pb/m of abstraction can be in terms of arms & motors. 2. 1-1/w & s/w Architecture : well before design. 3. Extra Inal Properties: Extra functionalities required in the stan being developed. 4. 8m Related Family of disigns : Families of related shows developed earlier should be taken into consideration during designing. 5. Modular Design: S/m designing 18 fast by decomposition of slw into modules that are to be implemented. -Modules should be clearly understood & should maintain continuity. - Appropriate protection strategies are necessary for each module. A module 18 not permitted to change or modely another module fnality. 6. Mapping: Mapping into various representations. For eq: deita flow in the same path during the program flow can be mapped together as a single entity. Transform & transaction mapping design processes are used in duigning. For eq; an image is 1/P data to a sm; it can have a

Scanned by TapScanner

User Interface Design: important part of design. For eq. in an Automatic Chocolate rending M/c 8/m, the uses iff is an LCD multiline graphics display. It can display a welcome mig as well as specify the coins needed to be inserted into the m/c for each type of chocolate it may be designed with touch screen Useeff. Réfinements: Each component & module design needs to be refined iteratively till it becomes the most appropriate for implementation by the s/w team. Development Process 1- adie alle alle supporter alles alles supporter alle alles parter Model/Analyse mon part Requirements of - Inthis inthe - to the K Design-Datastructure S/w Archi: 1/35 & Algons ycle Linear Sequence Inplementation design Chitrad & El Corro Test: Internal logic GExternal Ins. alites & albert Drafe of Const specifications lesign dueing an embedded

Scanned by TapScanner

Design Metaics: 1. Pouver Dissipation: For many 8 ms, battery operated 8 ms, such as mobile phone or digital camera the power consumed by the S/m 18 an imp. feature. The battery reeds to be recharged less frequently. 2. Performance: Instructions ean time in the stim measures the porformance. Smaller ex time means higher performance. 3. Process Devellines: These are no. of processes in the 8/m These have devellines which each of them may be required to finish computations & give results. 4. User interfaces: These include keypoid GUIS & VUIS. 5. Size: Size of the S/m is measured interms of (i) physical space required (ii) RAM in KB & internal flash memory equents in MB or CB. 6. Engineering Cost: Initial cast of developing, debugging & testing the h/w & s/w. 7. Manufacturing Cost: Cost of maneufacturing each cout. 8. Flexibility: Flexibility in design enables, without any significant engg. cost, development of deff. versions of palt & advanced versions later on. 9. Prototype: Time taken in days or months for developing the peopolype & in house testing for S/m fnalities. It includes engy. time & making the prototype time 10. Time to market: Time taken in days or months after prototype devpt to put a pat for cisers & consumers. Il System & user safety: S/m safety in terms of accidental fall from hand or table, theft & in terms of user safety

Scanned by TapScanner

Complex Systems & Microprocessors: Microprocessors: The CPU is a unit that contrally fetches E processes à set of general purpose instructions. The CPU instruction set includes instructions for date transfer op's, ALU op's, stack op's, 10 op's & pan ctel, sequencing op's. The general purpose math set is aboays' specific to a specific CPU. EPU must person the following basic functional curits. 1. A ctal "curit that fetches & ctals the seguental processing of a given command or inst? 2. An ALU undertakes authmetic Elegical 003 on bytes or words. A microprocessor 18 à single VISI chip that has a spit & some other units (eq: that g pt. unit, pipelining unit). Earlier generation processor's fitch & execute cycle was guided by a clock fr. of order of ~ 414th Now operate at clock fe. of 4 aHz. High performance processors have pipelin & super scalar architecture, Jast ALUS & floating pt. processing mots. The important uprocessors used in the embedded systems are ARM 80 x818 SPARC family of uprocessors. A general propose Processor Maria can be embedded on a VLSI chip. Diff. Steemi nf 11 honragenze

Scanned by TapScanner

Aprocessor family Source CISC or RISC or Both feature Stream Streaml G& HC XXX Motorda CISC Stream 2 80×86 Intel CISC Stream 3 SPARC Sun RISC Steern 4. ARM RISC with CLSC family ARM Abstraction of Steps in the Design Process; A design process is called bottom to top design if it builds by starting from the components. A design process is called top to down design if it starts with abstraction of the process & then after abstraction the details are created. Top to down is the most favored approach. 5 levels of abstraction from top to bottom in the design process. 1. Requirements. Définition à analysis of 8/m requirement. It is only by a complete clauty of the required purpose, inputs, o/ps, fining, design metrics & validation regionts for finally developed 3/ms specificts that a well designed slow can be created. 2. Specifications: Clear specifications of the required; s/m are must - precise, quide customes expectations from the product. Quide 8/m achitecture. The designer needs specifications for (1) k/w, eg: perspectals, devices, processor & memory specific's. ii) data types & processing specifications iii) expected 8/m behaviour specifications FV) constraints of design

Scanned by TapScanner

Aschitecture: Data modeling designs of attributes of data structure, data flow graphs, s/w architecture layors & h/w architecture are defined. S/w architectual layers are 1. 1st layer - architectural design: A design for 8/m architechine is def developed. \_ how the elastsdata structures, databases, algms, ctel fns, state trans Fns, process, data & pgm Show are to be organized. 2. Second layer \_ data design \_ Design of datastrution & databases. 3. Third layer\_Interface design\_Interfaces to integrate the components. Components: Component level design, -design of each component. Each component should be optimised for mem usage & pouver dissipation. Components of h/w, processes, i/Is & algms. Hardware components 1. faocessor & Single puepose processor in the s/m. 2. Memory RAM, ROM or internal & external flush or secondary memory. 3. Peripherals & devices internal & external to the sh 4. Ports & buses in the s/m. 5. Power source on battery in the s/m. System htegration: Built components are integrated in the Sm. Components work independently. Each compo nent q its ils smis integrated after the design stage. Program implementation 18 in a lang. & may use an integrated development Environment & source

Scanned by TapScanner

Challenges in Embedded System Design: Optimizing Design Metuics. Following are the challenges that arise during The design process. Amount & type of h/w needed: Optimizing the equat of uprocessors & single purpose processors in the s/m on the basis of performance, power dessipation, cost & other design meterics are the challenges in a s/m design. Optimizing Power Dissipation & Consumption: Power, consumption during the operational & idle state of slm should be optimal. The following methods are used to meet the design challenges. Clock Rate Reduction: Power dissipation typically reduces 2.5 UN per work Hz of reduced clock rate. So reduction from 8000kHz to 100kHz reduces power dessipation by about 2000W which is nearly similar to when the clock is non final. The power 25 MW is typically the residual dissipa tion needed to operate the timers & few other units. By operating the clock at a lower frequency or dearing the power-down made of the processor, the advantages are: i) Power loss due to heat generation reduces. ii) Radio frequency interference also reduces due to the reduced power dissipation within the gates. Voltage Reduction: In portable or hand-held devices such as a cellular phone, compared to 5V operation, a CMOS det power reduces by one sizeth, in 2.0 V Op?. The time intervals reeded for recharging the battery

Scanned by TapScanner

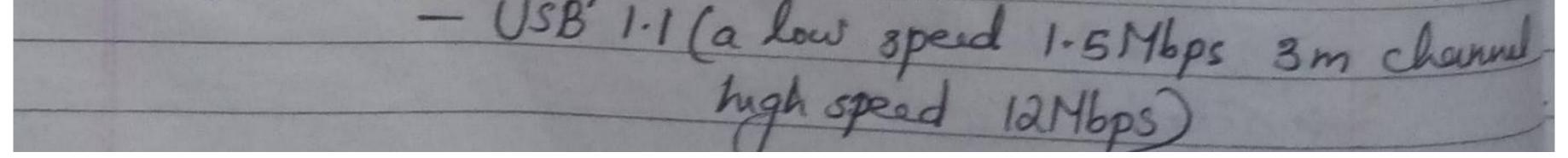

Wait, Stop & ache Drable Instructions: Total power consumption by the s/m while in sunning, waiting & idle states should be limited. A microconteoller must provide for executing what & stop instauctions for the power down mode. One way to reduce power dissipation is to incorporate into 8/w, the wait & stop instructions. Another is to operate the s/m at the lowest voltage levels in the idle state & selecting power-down mode in that state. Process Deadlines: Meeting the deadline of all processes in the 3/m while keeping the memory, power dissipation, processor clock rate & cost at min. is a challenge. Flexibility & Upgrade ability: in design while keeping the cost minimum Ewithout any engg. cost is a challenge. It provides diff. & advanced versions of a pdtto be introduced in the market. Reliability: Designing a reliable product by appeopliate design, testing & thoeough verification is a challenge. Embedded blu Components: Power Source: Most S/ms have a power supply of their own. The Network Interface Card & Graphic Accelenter are eq: of embedded s/m that donot have their own power supply. The supply has a specific range of voltages: 5.0V±.25V, 3.3V± 0.3V; 2.0V±0.2V & 15VE 0.2V . Low voltage Operations: the portable or hand-held devices such as cellular phone 2. Low voltage 3/m processors & 1/0 chts generate lesser

Scanned by TapScanner

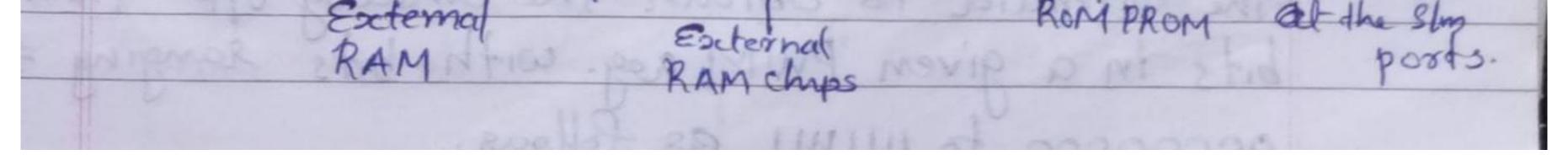

Clock Oscillator Circuit and clocking Units: - The clock ctels the time for executing an instruction The clock is the basic unit of a s/m. The clock controls the various clocking equits of the CPU, of the slim timers & the CPU m/c cycles. The m/c cycles are for fetching codes & data from memory & then decoding & executing them at the processor & for transferring The results to memory -System Timers & Real-time clocks: A timer ckt is configured as the sim-clock, which ticks & generates slos interrupts periodically. for eq: 60 times in 1s. A time clet is configured as the real time dk that generates s/m interrupts periodically for the Schedulers, real-time pans & for periodic saving of time & date in the Sm. The RTG on slow timer is also used to obtain she chelled delays & time outs. Reset credit, Howes-up Reset & Watchdog - Timer Reset: Reset means that the processor begins the processing of instructions from the starting address. That address is one that is set by default in the processor PG on a power up. A gon that is reset & sums on a power up can be one of the following: (i) A ston pgm that executes from the . Ad all been si to some begining. (i) A s/m bootup pgm (iii) A s/m initialization Meniozy: Syn System Memory Internal RAM Internal Caches Flash EPROM at lictellee Memory Addr. at upracessor

Scanned by TapScanner

Input, autput & 10 Posts; 10 Buses & 10 Interfaces clets. -> A recience of 8/2s from comm -8/m. -> Ports recience 1/ps from a n/w or peripheral The 8/m has O/p poots: 1. LED, 2. Printes 3. Communication s/m 4. Alarms, actuators & furnaces. 5. Various motors. Bus: A s/m might have to be connected to a no. of other devices & 8/m. A bus consists of a Common set of line's to connect multiple devices, R/w anits & s/ms for comm. DAC using PWWI and an ADC DAC 18 a cht that converts digital 8 or 10, 12 bits to analog output. The analog OP 13 W.J. to the ref. voltage. Pulse Width Modulator (PWM): with an integrator ckt 18 used for the DAC. -> Pulse width is proportional to the analog o/p needed. PWM i/ps are from 00000000 to minili for an 8 bit DAC pattern. pwm mut outputs to an ext. integrator, which provides the desided analog of From this inf. The formula to obtain the analog ofp from the

Scanned by TapScanner

Analog olp V=K. pu where K 13 constant & pw 13 the pulse width. Analog to Digital Converter 18 a clet about converts The analog 1/p to digital 4,8,10, by 12 bits. The analog i/p is applied blu the positive & - ne pins & 18 converted w.r. to sef. voltage. When ilp 13 equal to diff. of ref. the & -ve voltages, then all out put bits equal 1; when equals -ne set. voltage Then all opp bits equal 0. LCD, LED & Touch Screen Displays. A 8/m requires an i/fing clet & s/w to display the status or msg for a line, for multiline displays, or for flashing displays. An LCD screen may show up a multiline display of characters or also show a small graph or icon. A secent innovation in the mobile phone 3/m turns the screen blue to indicate an incoming call. To indicate the ON status of the slm, there may be an LED that glows. A flashing LED may indicate that a specific task 18 under completion or running status. A touchscreen is an ile as well as olp device, which can be used to aster a cond, chosen menu or to give exply. This info is input by physically touching at a screen par wing a finger or stylas. Keypeid/Keyboard:

Scanned by TapScanner

Interrupt Handler: A timing device sends a time-out interript when a preset time elapses or sends a compare interrupt outen the present time equals The preset time. An interrupt-handling mechanism must exist in each sho to handle interrupts from various processes & for handling mechanism must exist in each spin to handle interrupts from simultaneously pending for service. 1. An interrupt may be a how sll that indicates the occurrence of an event. 2. The s/m may prioritize sources & service them accordingly. 3. Certain sources are not maskable. E cannot be disabled. Some are assigned the highest priority during processing. 4. The processor's current pgm. has to devert to a service soutine to complete that task on the occurs of the interrupt. 5. These 18 a gymmable unit on chip for the interrupt handling mechanism in a licheller. 6. The OS 18 expected to ctel the handling of interrupts Examing of eautimes for the interrupts in a pasticular application. The stop give priority the ISRs over the tasks of an application."

# Scanned by TapScanner

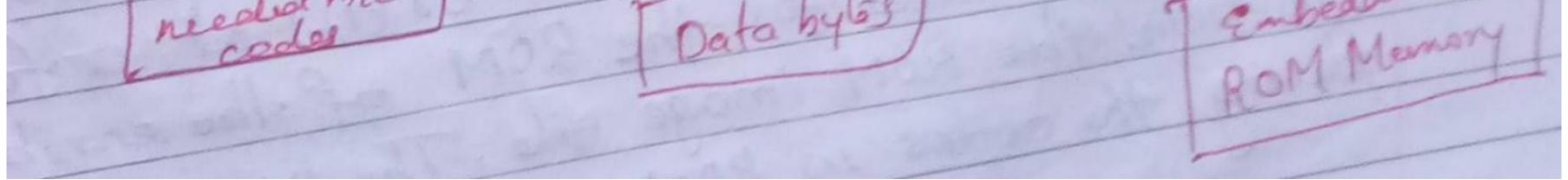

Software Components in an Embedded System Final M/c Implementable 8/w for a system: An embedded s/m processor executes She that is specific to given appl" of that slm. The inst" codes '& data in the final phase are placed in the ROM or flash memory for all the tasks that are executed when the s/m suns. The slu 13 also called ROM Image. Coding of Slw in Mlc Codes: Programmer defines the addresses & the corresponding bytes or bits at each address. For eg: in a transcrever, placing certain m/c code & bits can configure if to transmit at specific Mb per Bee - 08 Cibps, using specific bus & n/wing protouds -S/w in Processor Specific Assembly Language: A pgm or a small specific part cambe Coded in assembly long using an assembler after understanding the processor & inst" set. The specific Assembles For the ready. Device ROM Assembly Long (Burner) Linked Pary Linker From lebrary Jembedded Sm needed mlc Opto by 63

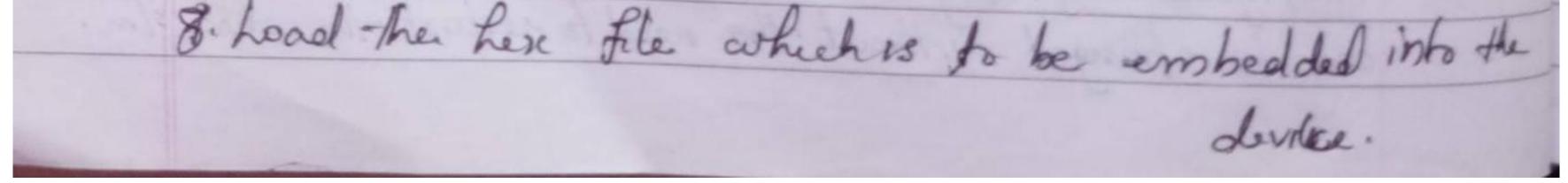

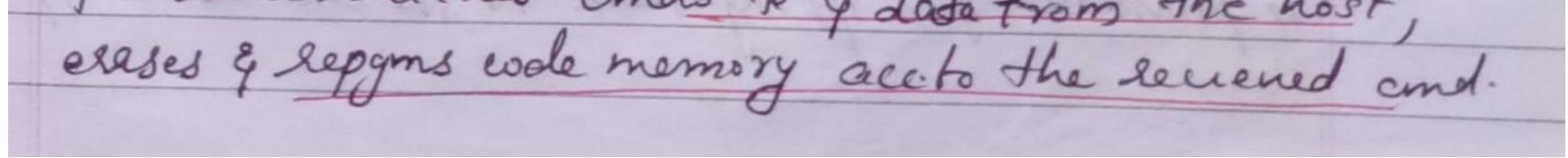

Process of converting an assembly lang. Pgm into mlc implementable sho file & then finally obtaining a ROM image file. OFn assembles translates the assembly she into the m/c codes using a step called assembling. Dh the next step, called linking, a linker links there codes with the other codes required. Linking is necessary ble of the no. of codes to be linked for the final binary file. The linked file in binary for run on a computer 18 known as an executable file or simply an i exe' file. After linking, there has to be reallocation of the sequences of placing the codes before actually placing the codes in memory. 3 Next step, the loader pgm performs the task of reallocating the codes after finding the phy memory addresses available at a given instant. The loader is a part of the O.S & places codes into the memory after reading the 'exe' file. (4). The final step of s/m design process is locating these codes as a ROM mage. The codes are permanently placed at the addresses actually available in the ROM. In embedded sims, there is no separate pgm to keep track of the available addresses at diff. times during the sun. (5) Lastly either (i) a laboratory s/m, called device pgmme takes as i/p the ROM image file & finally burns the image into the PROM or flash. or (ii) at a foundry a mask is created for the ROM of the embedded

Scanned by TapScanner

Software in High Level Language: Pretrocessor Commands Main Function The duff. pgm laye Interrupt Service Rachnes in the embedded Tasks 1 -- N sho in C. Kernel & Scheduler standard Library Ins including N/w protocol for for sending stack & Receiving Stack -shows the process of converting a c pgm into the ROM image file. A compiler generates the objt code It assembles the codes are to the processor inst" set E other specific's. The C compiler for embedded 8/ms, must, as a final step of complation, use a code - optimizer that optimizes the codes before linking. After complation, the linker links the objt codes with other needed codes M/c Codes in 3 Program Obt File Functions From Library Bytes for Needed M/c Linked Pamst Codes Embedded S/m ROM Memory

Scanned by TapScanner

Peggram Models for 8/w Designing: These models that are employed during the dirign prousses of the embedded s/w ase as follows: 1. Sequential Program Model 2. Objt Oriented Program Model Z Control & Dataflew Graph 4. Finite that M/c for data parts 5. Multitheaded for conculent processing. -> UML. Softwale for Concurrent Processing & Scheduling of Hultiple Tasks & ISRs using an RTas. The multiple tasks are processed most offen by the OS not sequentially by concurrently. Concurrent processing tasks can be interrupted for summing the ISR's, & a higher plionty task prempts the sunning of lower prionity tasks. OS 8/w have scheduling for for all processes in the s/m. Since the running of tasks and ISRs may have real time constraints & deadlines for finishing The tasks, an RTas 18 required in an embedded 8/m. The RTOS provides the as functions for caling the s/m, provides interprocess Commentings & ctals the paying of mags & s/ls to a task. Software for Device Drivers & Device Mymt in an O.S. - physical devices like times, key boards, display, flash memory, parallel ports & n/w cards. A par 18 also be developed using the concept of vistual devices. eg: A file, A pipe, A socket & RAM duk. A device driver is slw for opening, connecting or binding, reading, writing & closing stalling actions

Scanned by TapScanner

listen, read or write or close. A driver ctals 3 fns: i) Initializing, which is actualid by placing appropriate bits at the stal seq. or word. i) Calling an ISR on interrupt or on setting a status flag in the status eg & eunning the ISR. in Restarting Resetting the status flag after an interrupt service A device doiver accesses à parallel or serial port, key board, mice, clisk, slw, display, file, pipe & socket at specific addresses. Software Tools for Designing an Embedded 8/m for weiting codes or assembly mummer Eclipa : line by line translation to exe cudes Interpreter : source code to chject code. Compiler translating assembly memonics to Assembler binary opcodes. For converting obst codes or executable Cross Assembler codes for a processor to other codes for another processor . It allembles The assembly codes of the target processor as assembly cades of processor of the PC used in s/m development. To simulate all this of an embedded Simulator s/m ckt including that or additional memory & perphirals. : For source code comprehension, navigation Source code E browsing, editing, debugging, configures onog. g/w

Scanned by TapScanner

Safhvare Tools Required in Exemplary Cases: -> Edutor, Interpreter, Compiler, Assembler, Toeahr etc. (Table 1.3 27) Encamples of Embedded sins -> Washing m/c 3. Robotics 8/m -> Multitasking bys 4. Keyboard cheller.

MODULE II -> Hardware Software Co-Design & Program Modelling > Fundamental Issues > Computational Models - Data Flow Graph 62vr - Control Data Flow Graph 6.2 - State Machine 6.3~ - Sequential Modelvi - Concurrent Model - 6-2 gr - Object oriented Model Eg: 6.3V - UML 5.5

Scanned by TapScanner

Hardware Software Co-Design & Rigram Modelling. Development Process & Hardware - Software. Devpt Phase Hardwale Software Selection Assembly for Target 3/m Develop using Edit-Test-Debug Cycles Till Test Burge Test It/us K Results ok Reagenble on H/w on she Errors End Edit\_test\_Debug Cycle - Main Approaches: 1. An IDE or prototype tool 2. A simulator without any h/w 3. Processor only at the target 3/m & uses an in- blue 4. Target sim at last stage. Issues in Hardware - Safhvare Co-Dengn: There are 2 approaches for the embedded of design: 1. The SDLC ends and the liferyde for prove of integrating the spu into how begin at the time who

(2) Both cycles concurrently proceed when co-designing a time cartical sophisticated 8/m. The final design, when implemented, gives the targetted embedded sim & Thus the final product. - slw & h/w designs & integrating both into a - h/w s/w codesigning are important aspects of designing embedded s/ms. The selection of the right h/w during h/w design & an understanding of the possibilities & capabilities of hhu during Shu design is critical. 1. Choosing Right Platform: - Software Hardware Tradeoff: - H/w implementations provide advantages of processing speed. Certain substme in h/w (cteller, 10 memory access clet, realhine clk, s/m clock, pulse width modulation, times & secial comm) are implemented by S/W. H/w implementation provides the follo other adviges: i) Reduced memory for the peogram. 2) Reduced no. of chips but at em increased cost 3) Simple Cooling for the device drivers. 4) Internally embedded codes. S/w implementation provides the follo. adv: D'Easier to change when new h/w versions become available. 2) Programability for complex operations 3) Faster development time 7) Less cost for simple 8/ms. 4) Modulanty & postability

Choosing a right Platform: A platform consists of a no. of units. Plocessor, ASIP, Multiple processors, System on Chip, Memory, H/w units of 8/m, Buses, 8/w language, RTOS. Cocle génération tools. Embedded System Processors Choice: D Processor-less System: PLC can be used in place of processor. PLC can be used for the clothes-in clothes out type 8/m. A PLC has very low op speed. It also has a very low computational ability, very strong ilfing capability with its multiple ups & olps. Automatic Chocolate-rending m/c can be another application of PLC. 2) Systems with Microprocessor or Micro controller or DSP. 3) System with Single - Purpose Processors in VLSI or FPCAD The processing of fins by using IPs embedded into VLSI instead of processing ALU - Display Unit Mprocentit 17 Menery - Input Unit Udulles/DSP PLC Unit - Communication Unit 1/8 Logic or multipracesser L Memory Unit Pisplay Unit Power Supply Unit Input Unit Appl Specific 1Ps for USB Menory Inst Processors OT TCP/IP or Pot Stark

Scanned by TapScanner

D'Factors & Needed features taken into Consideration: Mensong & Recessor - Sensitive f/w: Peocessor Sensitive: 1/0 instructions are peocessor sinsitive A processor may be having fixed pt. ALU only. Floating it. opn's when needed are handled differently them in a processor with floating pt. operations. A processor may not provide for exa of Single Inst Multiple Data (SIMD) & VLIW (very Large Inst Word instauctions. Memory. Sensitive: Eq: video processing & real time video processed/sec will depend on memory available as will as the processor performance. If a large memory is available then higher resolution pictures can be processed. - Memory address of 10 device registers, biffers, chil registers & vector addresses for the interrupt sources or source groups are prefixed in a platelles. ~ Allocation of Addresses to Memory, Pgm segments & Deviles: Program routines and processes can have diff segments. For eg; a pgm code can be segmented & each segment stored at a diff. memory blk. A pts points to the start of the memory blk storing a segment & an offset value is used to returne a memory adds. within that segment. Dévice, Internal Déviles & 1/0 Dévile Addresses & Dévile Drivers: All 1/0 ports & devices have addresses; These are allocated to the devices ace to the s/m processor &

Scanned by TapScanner

processors. A device has ana address, allocate to the follo 1. Device data Registers 2. Device del register: il saves del bits & may save config bitsalse 3. Device status registers: It saves flag bits as device statu Parting Issues of OS in an Embedded 3/m: -1/0 Instructions: A port instruction data type may be deff on the deff. platforms. - Interrupt servicing contines: OS supports these diffy on diff platforms - Data types: Appropriate API's for datatypes. - Interface - specific data types: Eq: Nfw 1/4 Card support 32 bit unsigned integers. - Byte Order, Data Alignment, Linked lists, Mem-pag Size, Time Intervals. Performance & Performance Accelarators: Performance Modelling: 1. 3/m performance Index: can be defined as the ability to meet egd. for & specifications while using the min anount of resources of memory, power dissipation & devices & min. design efforts & ophimum ablezation of each resource. 2. Multiprocessor Slm Performance: is measured by i) an optimized partition of the pgm into the tasks or set of inst's blue the various processors (i) an optimized scheduling of insta & data over the available processor times & resources. 3. MIPS, MFLOPS & DMIPS as performance Indices: One

Scanned by TapScanner

MIPS - Million Inst's Per Second MFLOPS - Million Floating Pt Inst's persecond DMIPS - Dheystone million Inst's per second. 4) Robermance Metoics: Buffer Requirement, 1/0 Performance & Bandwidth Requirement. Lacelasetes performance 5) Real Time Pgm. Performance: Dratio of sum of interrupt latences as a In of the exa times 2) CPU hoad 3) worst case ex w.r. to the mean exh time. Performance Decelarators: - Conversion of CDFC13 to DFC13. - Reusing the used arrays & memory, appropriate variable selection, appropriate memory allocation deallocation strategy. - Using stacks as datastructure when feasible instead of queue & using queue instead of list - Computing slowest cycle. first & examining the possibilities of its speed up. Computational Models: -> Polling for events model. These is polling in cyclic loop for the events, state variables, msgs & slls using the switch-case stats. -> Sequential Program Madel: sequential paming model in which there are sequential multiple for calls within a function. -> Data Flow Model: used for modelling the data paths, and pgm flows of s/w. A pgm is modeled

Scanned by TapScanner

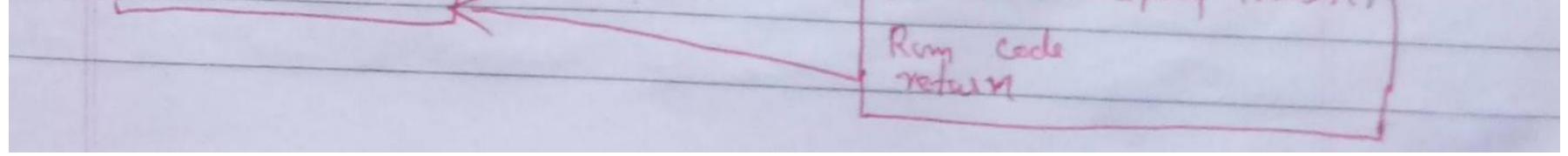

State Machine Model: A pgming model 13 that there are deff. states & the model considers a s/m as a m/c., which is producing the states. Program sequentially polled for the screen state & menu choice selected by the uses. -> Concurrent processes & Interprocess Communication Sequential Program Model: Example. function f1 Call fi Rom code return Multiple In calls function for call f2 Run code return The server so Coull f3 function f3 Ren Code LON MAN COL and in the part Setun Eg: Sequential Programming model of an ACVM: function get user ypc) Rem tode return function read-coins() Sequentia Run code Sunction calls return while 22 get used i/p(); function delive-chlouters nead coinsi?; Run code so) deliver chocos; return display thomks (); 3 Function display. Thomas ()

Scanned by TapScanner

Run function get-uses inputes for obtaining ile for the choice of chocolals from the child. -> Run hinchon read coms () for reading the coms inserted into the ACVM for the cost of chocolate. -> Run Runchon delive-chocolaters for delivering chocolate. -> Run function display thanks() for displaying collect the nice choeolate , visit Again " Data Flow Graph & data flow means that a program flow & all pgm execution steps are determined specifically only by the data. She designer predetermines the data Ups & designs the pamming steps to generate the data o/p. Far eq: a program for finding an avg of the grades in various subjects will have the data itps of the grades & data O/P of the avg. Data that is input after the op's in the pgm becomes data that is ofp after a data flow . A diagram called DG DFG represents this graphically. There is only one independent path for the pgm flow when the pgm 18 executed. -A circle represents each process in DFG. An accow directed towards the circle represents the data No & an aclow originating from the circle represents a data op. Data ip along an up edge is considered as token. An Up edge has at least one token. The viele Represents the node. The ofp is considered by the outgoing

Scanned by TapScanner

Eg: An oth fillered culput sequence, 1/nº 2(9; 2mil) where the sum is made for 120,1,2 ....... following are the pts. notable for the process of collecting 's = as 26 tap 20 tap 24 tag 23 tag 2 2 tag 2 2 tag 2 1. There is one ile pt. to the present - +aling represented by the circle for calculating you 2. Those is one of pt. for 16 3. There is only one memory address if theighte for each welficient & each filler 1/2. There is only one Value of each of the size y/ps for se & there is only one value of each of the coeff.a. The order in which sps are obtained & summation 13 done is also immaterial. ao a a.s. au 02 Dutaingo an a, 15 ) 5m) 902679,21 an 42×4+ 43×3 YE 34 245 I, DL where a = atb Data Elswrods Data flow node

Scanned by TapScanner

DFG model for pgm for a sarring a picture is a degetal camera. task read frame status & data of task for all or & y pixels laving the CED COof image frame data of pixels processor back area & an exposured at feame for computing columns at cep mem. buffe & subtracting Co pascesser offsets in pictule alla prices task JEG Compression DFG madel pgm translates & executes as a single process seq. model pgm. A pgm executes as per 1/p of the ip determines the opp. Software implementation becomes greatly simplified when using the DFCrs b/c in the DFCr model, there is a single deta-in point and a single data-out point, with a process or set of processes that are represented by et circle. Programming tasks are simplified by representing the code for each process by a circle, using the data input From incoming arrow & generating data output along outgoing arows - When the assignment to an 1/p & forced in a DFS, it is called ADFG (Acyclic DFG). Programming Complexity is minimized by modeling a pgm in

Scanned by TapScanner

ADGIF ADFUS as possible. Conteol DFor Model A ctel flow means that specifically only the pgm determines all pgm en styps & flow of the pgm. The s/w designer pgms & predetermines these steps. A process may have the starts that chil the i/ps or o/ps-It may have loops or condition starts in blue. Data that is 1/12 generale the data ofp after a ctel data flow as per the Attiling conditions. Output depends on the ctel stats for various decisions in a process. A core 18 a diagram, which graphically represents the cond's & the pgm flow along a condition dependent path. A circle also represents each process Called node) in a CDFC. A directed allow towards the circle represents the data ip & directed about from the ciècle represents à data dp. A box may represent a condition. A condition can be marked at the start of the directed arc or arrow. A directed arrow from the box or a marked starting condition determines the action to be taken when the cond 15 true. Escample: The stalling i/ nodes by the test cond specifying boxes, & the data 1/Ps to a CDFG for an filter with 10 1/ps & 10 coefficients; yn= 2(a; 2(n-i)) Following are the pts. notable for the process of calculating yn. There is one i/p pt. to the proce represented by the circle for calculating yn. 1. There is one ofp pt. for yo There is only

which take multiple values during the sam flow, 2. The order in which iles are obtained & summiting 15 done does mottes. [3: 12 Alagel, 7 = 0 46 1/2 /m 1/20 20 11.11 10 as a1 - age 203, 30 2= ·1 · 1 · 1 · 1 a Train test 220 1-3. 120 SECHE n=11-1 NO 19 n=n-1++ Data 1/25 & ctilling 1/2 nodes shown by test boxes in a ctal Ofor for a finite impulse Rupons (FIR) filter with 10 1/ps & 10 Coefficients Interrupt ant interrupt 3/m enable mastrea Execute Read Port A Fishi post A. mquese interrupt

Scanned by TapScanner

> Synchronous Data Flow Graph Model (SDFG) When there are no. of tokens required for a computation to generate more tokens in a single firing, The data flow is said to be synchronous. The SDFC model is as follows. Let an arc represent a buffer in physical memory. The age can contain one or more initial tokens with the delays. A token doesn't fire the computations at a vertex till it is reciened at the vertex. Vertices (ciscles) in this graph are called the acloss. Actors do the computations. An actor also sepresents a complete DFG within itself. An edge blu the vertices represents à queue of output values from one vertex & a greve of i/p values to another vertex. Edges carry values from one actor to another. Let X & Y be a sets of instructions that once started, do not need any further 1/ps from any source during the computations. Let X generate the op values a, b, &c. Let Y get the 1/2 values a, c, i & i and let i have a delay. The no. of 4/PS to Y need not equal the no. of o/ps from X.Y gets additional ips and doesn't need all the ops from X. These computations & data are now modelled by a directed DFG that exist from X to Y. Verties (Actory for Computations a, g;j) (a,b,c) 3 The no. of outputs & i/ps are labelled near the arc origin & arc end. Fig shows actors (values, which does the computations on fixing) and acce in a directed

Scanned by TapScanner

An SDFC1 model 10 like a DFC1, but also models the delays as well as the no of yps & 0/ps. The edges directed to the circle can be assumed to have a phy. mem. buffer ? till the buffer has the data, the computations donot fire. Concurrent Model A pamming model is that there are several concurrent tasks & each task has the sequential codes In infinite loop. A task sends a mag or s/l for another task. A task, which gets a msg or s/l, sums & the remaining tasks remain in the blocked state. Eg: Concurrent eurning of the processes in ACVM. 1 ISR Coul\_interrupt() process get\_user\_inputes Ran\_code want GUIInterrupt Msg Concisent processes create Run code Signal Sread-coins Signal cristerrupt Mg create process get\_usel-input; process sead-coinsc) process deliver-chocolater create process wait Sdeliver-chocolati want Seead - coins read-coinsc); Run code Kun wale create placess Signal Solehner-chocolate deliver chocolates; Signal Schisplay \_ thomas create process Signal Sdupplay want display\_ thankscs; process display-thinks() create process process desplay-water Wait Sdisplay - went Wait Sdisplay - themses wait Sdrippay- thates display\_wortes; Runcode - Collect the nice chocolete" Wait Sduppery-wait Signal Soluplay - thanks Signal Sduplay\_wait Derows Show inter-process communications. The pgm consists of follo. processes, which can un

Scanned by TapScanner

1. Process get-user-i/p() for obtaining 1/p for the choice of chocolate from child & sking to process read-coins start. 2. Process read-coinses want for sll get-uses-eppeter & stast reading on s/l from for reading the wins inserted in the ACVM for the cost of chocolate. Posta 3/2 to process deliver chocolate to start & also past a s/l to process 3. Process deliver-chocolaters wait for s/l from lead-coinses & starts delivering the chocolate & past a sll to display themks () b start. 4- Process display-warts for s/l from read-coins() 9 starts displaying " wait few moments ' & then wait for s/l for deplay-thomks(). 5. Process display thanks () waits for 8/2 from deliver-chocolater, and from display-waites & starts displaying Collect the nice chocolale, "visit Again!" Object Oriented Revgramming Model: Main features: a. when there is a need for reusability of the clefined objt or set of objts that are common within a program or blu many applications; when there is a need for abstraction & when by defining objts by inheritance of polymosphs, new objts can be created: There is data encapsulation within an objt. b. In objet is characterized by its identify, by its state, E by its behaviour Cop's Emethods, fields & attributes j Defining the logically related groups makes a class. Class defines the state & behaviour. If has internal user level fields for its state & behaviour. It defines the methods of

Scanned by TapScanner

d) Objects are created from the instances of a class. A class can thus create many objects by copying the group & making it final. Each object is functional. Each object an interact with other objts to peocess states as per the defined behaviour. Erample: Classes & objts: 1. Class CNI for graphic-user interaction. It has a methods display menues & get-user-i/pes & for obtaining Mp for the choice of chocolate from the child. It has method set-choice () to set the choice selected. 2. class Read-coinsc ) for leading coins inserted. I has a method read , to read one, 2 & 5 rupee coms from 3 posts & method sum() for summing the total. wins. 3. class Delever chocolate. It has methods get-choiles to get choice & deliver () for delivering the chocolate. 4. Class MsgDisplay. It has methods dieplay-waite E display - themkese, for displaying wait & thank megs. class civi is used to create civi objts as multiple instances of CNUI. Class MsgDisplay 13 used to create mg display objts as multiple instance of wait & themks migs. Class NegDisplay can be interfaced to an interface. steen-size(), which has an abstract method screen-size(). Extending class MsgDisplay can specify a new class MsgTime-Display. Extended class Mg Time-Display inherits all attributes 5 methods of class MegDisplay.

## Scanned by TapScanner

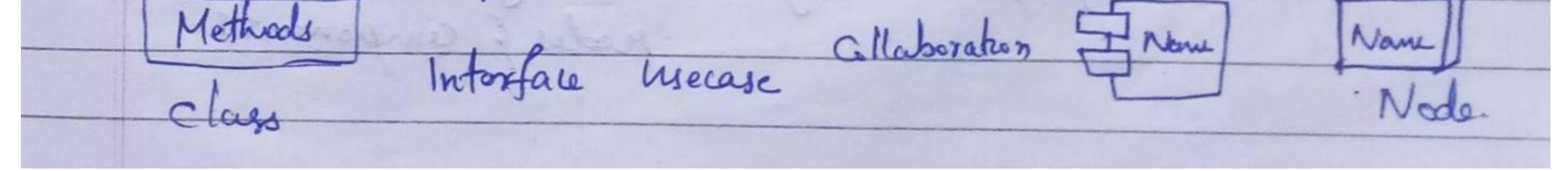

pagte: Lig: 6.3 UML Modelling general 8/m for which objt oriented analysis & design are feasible & which can be abstracted by models. Dragans: 6 Basic UNL elests: \* class \* package, steeestype, object, anonymous obje and state. Table 6.2, 6.3. Fig: 6.17, 6.18. the UML approach. It. can use the user, object, sequence, state, class & activity diagrams. UNL allows the Specchasts & Statechaets: Specthests 18 another lang. for specifications & cheats. It allows state m/cs to use seq. pgms to model the state actions. State Chart 13 a long. For implementing the actually diagram, FSM states & state transitions, concurrency Synchronization, timing & behavioral heerachy. Stabling MCL SML Scie One. in State M/c Pgmming Models . A state m/c 18 a model in which it 19 assumed that there are states & state transitions fins, which produce the states. A state transition fra. 18 a fr arhich changes à state to its next state. Zg: the literation

Scanned by TapScanner

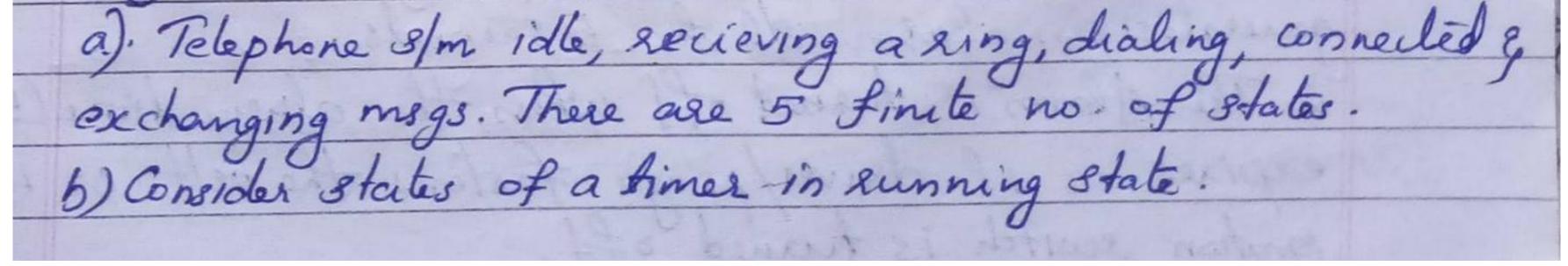

Times idle Times start Times summing - 2 - 1 Load 1/P Durseme 1/P 0/P Counterment Murey Ontput Dresement Count=0 I me out flag = get Figure shows the states of times by circles of state transition by acrows. The count i/p 13 the clock 1/p. The changed count value is the output. The old the is the ind increment in the count value. The state transition is the time out on overflow when a prede The State M/c model 13 used for modelling reating or event driven embedded sims whose processing behaviors are dependent on state transitions. The state Mc model describes the 3/m behaviour with 'states', "Events' & (Transitions'. State is a reps of a current situation. An event is an ilp to the state. The event acts as stimuli for state transition. Transition is the movement from one state to another. Action is an activity to be performed by the state m/c. A Finite State M/c (FSM) 15 one in which the no. of states are finite. Eg: An Enbedded s/m for drives/passenger Geat Belt Warning' in an automotive using the FSM model. The 8/m squets: The 8/m rgmts: 1. When the vehicle grition is turned on & the seat belt is not fastoned within 10 seconds of ignition ON, the sim generates an alarm off for 5 seconds. 2. The Alarm is turned off when the alarm time (55)

Scanned by TapScanner

Ignition Key ON Alam Walting gnition key off Seat Belt ONI Alam Grub set in anie Alaem ON Reg of the Alaem ON Temer ACVM, Automatic Tea/coffee Vending M/c, Coin Operated Public delephone Unit. Automatic Tea/coffee Vending M State A: Wait for Event: Tea Dispensed Statec CEIN Achon: Done Stale B: Wast for User 1/p State A Event Acher OK State A Event Connel State State A chas: com out State State A chas: com out Acher But Reast Co Pleas Dispensed Di state C: Dispense Tea State D' Dispinse Coffee. Eurit: Coffee Button Press Achon Dispense State Actes Done Jan - V UML Modelling Cost. -> Things, Relationships & Diagrams. Things -> Structure | Things : represents static parts of a VML model. Zg: Class, Interface, Usecase, Component, node, Collaboration egek. 1 dentifier Name) Component (Norme) Variables

parent Realization - realizes the behavious specified by the Elust 0 other elmit. A Elota. UML Dragrams! Static Diagrams - represents static/structural aspects. Eg: objt Digram - set of objts & relationships. Class Diagram - Classes, their iffs, interactions & relships. Component Diagram - Impl" view of a sim. Package Diagram - Packages & their elmts Deployment Diagram - Configh of hum time plocesing

Scanned by TapScanner

Use Case Diagram: S/m frality as seen by users. - cisecases & actors. Sequence Drage

| M/G  |  |

|------|--|

| 2/31 |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

## NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

Nistie

Reg. No.

(Approved by AICTE, Affiliated to KTU University, Kerala) SRIES TEST - 1 (2018-19)

CS 404 Embedded Systems

| Semester: VIII       | Programe: B.TECH       | Max.Mark:40     |               |

|----------------------|------------------------|-----------------|---------------|

| Course Code & Name:C | s 404 Embedded Systems | Duration:90 min |               |

| Knowledge Level (KL) | K1 : Remembering       | K3:Applying     | K5:Creating   |

| Course Outcome(COL)  | K2: Understanding      | K4: Analysing   | K6:Evaluation |

## PART-A

Answer ALL Questions (4 x 3 = 12 Marks)

| I. D         | efine a system and an Embedded System.                                                                                                                                                             |           | KI/COL           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|

| 2. Li        | st three main components of an Embedded System.                                                                                                                                                    |           | K4/CO1           |

| 3. W         | rite short notes on Computational models.                                                                                                                                                          |           | K4/CD2           |

| 4. D         | efine Control Data Flow Graph.                                                                                                                                                                     | -         | K1/CO2           |

|              | PART-B                                                                                                                                                                                             |           |                  |

|              | Answer ALL Questions (2 x 14 = 24 Marks)                                                                                                                                                           |           |                  |

| 5 a.         | Demonstrate the role of individual components involved in                                                                                                                                          | a typical | K6/CO1           |

|              | embedded system.                                                                                                                                                                                   | 4 Marks   |                  |

|              |                                                                                                                                                                                                    |           |                  |

|              | OR                                                                                                                                                                                                 |           |                  |

| 6 a.         |                                                                                                                                                                                                    | 4 Marks   | K6/C01           |

| 6 a.         |                                                                                                                                                                                                    | 4 Marks   | K6/C01           |

| 6 a.<br>7 a. |                                                                                                                                                                                                    |           | K6/CO1<br>K4/CO2 |

|              | Explain the challenges in Embedded System design. 14<br>Analyze the characteristics of different Program Models. 10                                                                                | Marks     |                  |

| 7 a.         | Explain the challenges in Embedded System design. 14<br>Analyze the characteristics of different Program Models. 10                                                                                | Marks     | K4/CO2           |

| 7 a.         | Explain the challenges in Embedded System design.       1         Analyze the characteristics of different Program Models.       10         Classify different State Machines with example       4 | Marks     | K4/CO2<br>K5/CO2 |

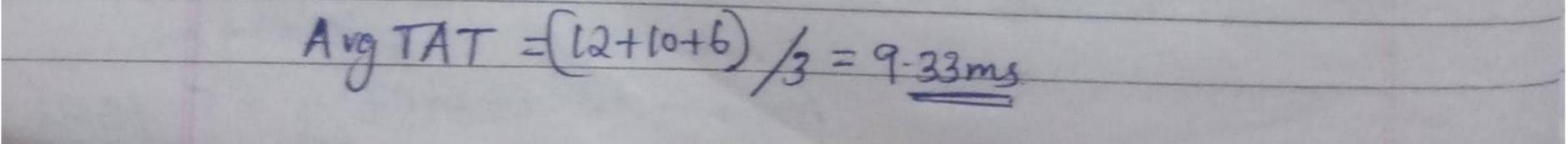

## Scanned by TapScanner